SV4E-I3Cを使用して、SPD(Serial Presence Detect)デバイス、ハブ、RCD(Registered Clock Driver)、PMIC(Power Management IC)、TS(Thermal Sensor)デバイスの完全なエクササイズとデバッグが可能に

、カナダ・モントリオール発 - 高速デジタル・アプリケーション用テスト/計測ツールのリーディング・カンパニーであるIntrospect Technology社は、JESD403-1 JEDECモジュール・サイドバンド・バス規格(以下、SidebandBus)に基づくデバイスのデバッグおよびテストのための高度な機能を追加したことを発表しました。SidebandBusは、DDR5メモリモジュール以降のシステム管理のためのプロトコルを定義した規格です。SidebandBusは、Introspect Technology社がコントリビューターメンバーとして参加しているMIPI®アライアンスと共同で開発され、MIPI I3C BasicSMバス規格のスーパーセットを提供しています。最も注目すべきは、SidebandBusは、バスの完全なスループットを犠牲にすることなく、バス上のサポートされるデバイスの数を増やすハブ機能を導入していることです。

、カナダ・モントリオール発 - 高速デジタル・アプリケーション用テスト/計測ツールのリーディング・カンパニーであるIntrospect Technology社は、JESD403-1 JEDECモジュール・サイドバンド・バス規格(以下、SidebandBus)に基づくデバイスのデバッグおよびテストのための高度な機能を追加したことを発表しました。SidebandBusは、DDR5メモリモジュール以降のシステム管理のためのプロトコルを定義した規格です。SidebandBusは、Introspect Technology社がコントリビューターメンバーとして参加しているMIPI®アライアンスと共同で開発され、MIPI I3C BasicSMバス規格のスーパーセットを提供しています。最も注目すべきは、SidebandBusは、バスの完全なスループットを犠牲にすることなく、バス上のサポートされるデバイスの数を増やすハブ機能を導入していることです。

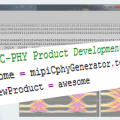

Introspect SV4E-I3Cテスト・デバッグ・モジュールは、すでに数年前から発売されており、I3C v1.0、I3C v1.1、I3C Basic v1.0を含むMIPI I3CSM仕様に対する成熟したテストおよび測定の実装を実現しています。今回のソフトウェア・リリースでは、JESD403-1に加えて、Serial Presence Detect Device Standard(JESD300-5)なども完全にサポートしています。

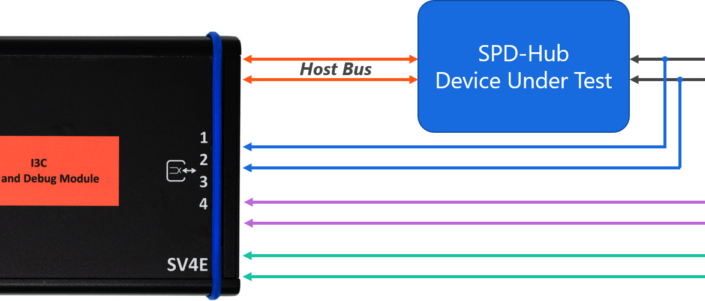

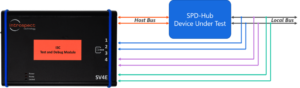

SV4E-I3Cは、JESD403-1およびJEDECデバイスのサポートにより、PMIC、SPD Hub、TSなど、DDR5のエコシステムに焦点を当てたデバイスを個別に演習する機能を提供します。また、R-DIMMなどのフル実装されたメモリ・モジュールを制御・解析する機能も備えています。例えば、1台のSV4E-I3Cは、複数のマスターおよびスレーブ・デバイスを内部でインスタンス化できるため、SPD Hubを完全にキャラクタライズするための理想的な自己完結型ソリューションとなります。この設定では、SV4E-I3Cのマスター・インスタンスは、SV4E-I3CがメインのSidebandBusホスト・コントローラであるかのように、SPD Hubを駆動することができます。また、SV4E-I3Cのスレーブインスタンスをハブの反対側に接続し、PMICや熱センサーとして動作させることができます。このようなエンド・ツー・エンドの機能により、初期のプロトタイプからシステムレベルのリグレッション、大量生産に至るまで、製品開発のすべての段階において、設計と故障を完全にカバーすることができます。

DIMMのテストでは、SV4E-I3Cは非常に直感的なSidebandBusコントローラ・プログラミング・インターフェースを提供しています。SV4E-I3Cは、リグレッションテスト、バーンインテスト、量産テストなどに最適です。

SV4E-I3C I3Cテスト・デバッグ・モジュールの主な特長は以下の通りです。

Introspect ESPソフトウェアを使用した操作:テストの開発と自動化のための受賞歴のある統合開発環境

デバイスの役割。SV4E-I3Cは、異なる役割(メイン・マスター、セカンダリ・マスター、スレーブ)を持つ複数のデバイスを同時にコンフィギュレーションできます。

デバイス・インスタンス。SV4E-I3Cは4つの並列デバイスを統合し、それぞれが独立したプロトコル・スタックを持ちます。

タイミング分解能:遅延生成(エクセサイザー)およびタイムスタンプ(アナライザ)ロジックのナノ秒分解能

プロトコル解析:プライベート通信、デバイス間通信、IBI、ホットジョインなどのCCCやパターンを容易にトリガー可能

SV4E-I3Cの詳細については、「SV4E-I3C」をご覧ください。また、Introspect ESPソフトウェアの詳細については、Introspect ESPソフトウェアをご覧ください。